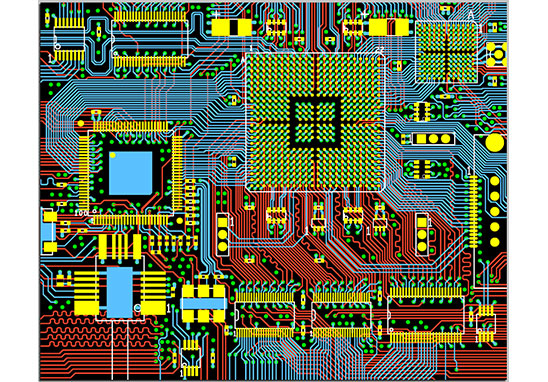

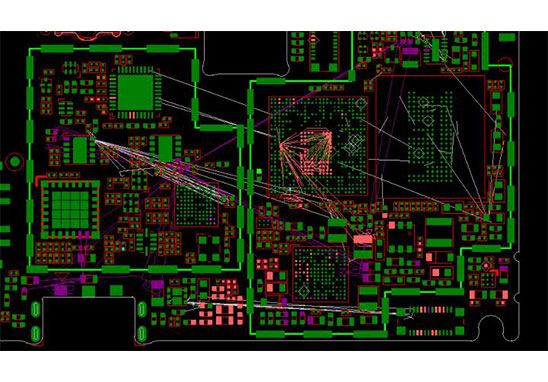

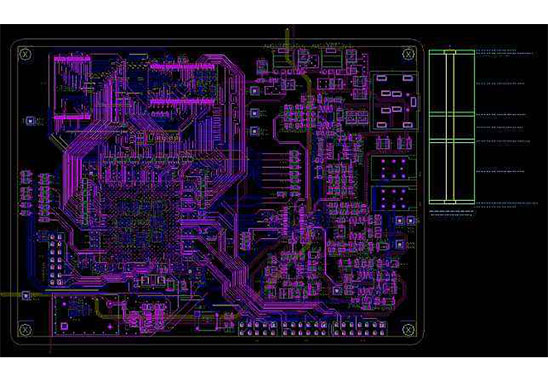

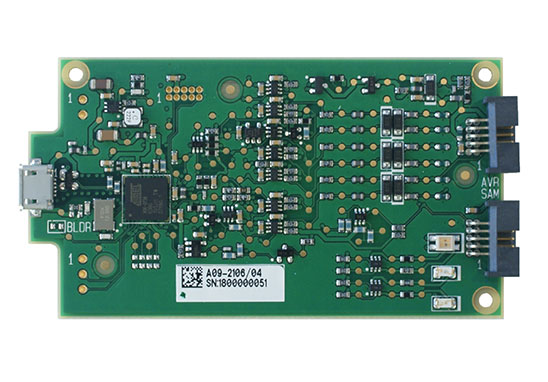

深圳宏力捷電子是一家專業(yè)從事電子產品電路板設計(layout布線設計)的PCB設計公司���,主要承接多層�����、高密度的PCB設計畫板及電路板設計打樣業(yè)務�����。接下來為大家介紹PCB設計如何做好接地設計����?

接地無疑是PCB系統(tǒng)設計中最困難的問題之一���。盡管其概念相對簡單����,但實現(xiàn)起來很復雜,并且不幸的是����,它沒有一種可以用詳細步驟描述的簡潔方法來確保良好的結果,但是如果某些細節(jié)處理不當�����,則可能導致頭痛�����。

對于線性系統(tǒng)�����,地面是信號的參考點����。不幸的是�����,在單極電源系統(tǒng)中,它也作為電源電流的環(huán)路被ACTS占用�����。接地策略應用不當可能會嚴重損壞高精度線性系統(tǒng)的性能�����。

接地對于所有模擬PCB設計都是重要的問題����,在基于PCB的電路中正確實現(xiàn)接地也同樣重要。幸運的是����,PCB環(huán)境中固有一些高質量的接地原理,尤其是接地層的使用���。由于此因素是基于pcb的模擬PCB設計的顯著優(yōu)勢之一���,因此在本文中我們將重點介紹它。

我們必須管理接地的其他方面����,包括控制可能導致性能下降的雜散接地和信號返回電壓�。這些電壓可能是由于外部信號耦合�,公共電流引起的,或者僅僅是由于接地線中的IR電壓降過大所致�����。正確的布線��,布線的大小以及差分信號處理和接地隔離技術使我們能夠控制這種寄生電壓����。

我們將討論的一個重要主題是用于模擬/數(shù)字混合信號環(huán)境的接地技術。實際上���,高質量的接地問題可以而且必須影響混合信號PCB設計的總體布局原則�����。

當前的信號處理系統(tǒng)通常需要混合信號設備���,例如ADC����,DAC和快速數(shù)字信號處理器(DSP)。由于需要處理具有寬動態(tài)范圍的模擬信號,因此必須使用高性能ADC和DAC�����。在惡劣的數(shù)字環(huán)境中保持寬動態(tài)范圍和低噪聲與采用良好的高速電路PCB設計技術密切相關�����,包括適當?shù)男盘柌季€�����,去耦和接地��。

在過去�,“高精度,低速”電路被認為與所謂的“高速”電路不同��。對于ADC和DAC���,通常將采樣(或更新)頻率用作判別速度標準�����。但是����,以下兩個示例表明,實際上����,當今大多數(shù)信號處理技術都是真正的“高速”,因此必須將其視為保持高性能的此類設備�����。 DSP�����,ADC和DAC都是如此�����。

所有適合信號處理應用的采樣ADC(帶有內置采樣保持電路的ADSC)均以具有快速上升和下降時間(通常為納秒)的高速時鐘工作����,即使吞吐量似乎是低。例如�,一個中速12位逐次逼近(SAR)ADC可以在10 MHz的內部時鐘上運行,采樣率僅為500 kSPS�����。

Σ-ΔADC具有高采樣率���,因此也需要高速時鐘���。甚至吞吐率范圍從10 Hz到7.5 kHz的高分辨率所謂的“低頻”工業(yè)測量ADC(例如ad77xx系列)也可以在5 MHz或更高的時鐘頻率下工作,并提供高達24位的分辨率�����。

更復雜的是�����,混合信號IC同時具有模擬和數(shù)字端口����,因此如何使用適當?shù)慕拥丶夹g就變得更加復雜。此外�,某些混合信號集成電路的數(shù)字電流相對較低,而其他混合信號集成電路的數(shù)字電流較高����。在許多情況下�,這兩種類型的IC需要不同的處理以實現(xiàn)最佳接地�����。

數(shù)字和模擬PCB設計工程師傾向于從不同角度看待混合信號設備��。本文的目的是說明適用于大多數(shù)混合信號設備的通用接地原理�����,而無需了解內部電路的細節(jié)����。

從上面可以明顯看出,沒有關于接地問題的快速手冊�。不幸的是,我們無法提供能夠保證成功接地的技術列表���。我們只能說忽略某些事情可能會導致一些問題�。在一個頻率范圍內有效的內容可能在另一頻率范圍內無效���。需求也有沖突����。解決接地問題的關鍵是了解電流的流向。

深圳宏力捷PCB設計能力

最高信號設計速率:10Gbps CML差分信號�;

最高PCB設計層數(shù):40層;

最小線寬:2.4mil�����;

最小線間距:2.4mil�;

最小BGA PIN 間距:0.4mm��;

最小機械孔直徑:6mil����;

最小激光鉆孔直徑:4mil;

最大PIN數(shù)目:63000+����;

最大元件數(shù)目:3600;

最多BGA數(shù)目:48+��。

深圳宏力捷推薦服務:PCB設計打樣 | PCB抄板打樣 | PCB打樣&批量生產 | PCBA代工代料