PCB設(shè)計是集成電路應(yīng)用設(shè)計中一個至關(guān)重要的環(huán)節(jié)����。設(shè)計結(jié)果的優(yōu)劣直接影響整個設(shè)計功能��。因此��,合理高效的PCB Layout是芯片電路設(shè)計調(diào)試成功中至關(guān)重要的一步�。接下來深圳PCB設(shè)計公司宏力捷電子為大家介紹PCB Layout的設(shè)計要點(diǎn)。

PCB Layout的設(shè)計要點(diǎn)

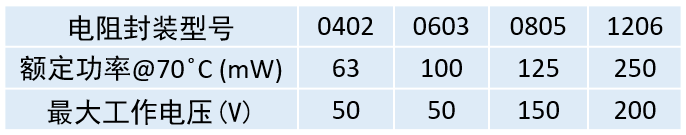

元器件封裝選擇

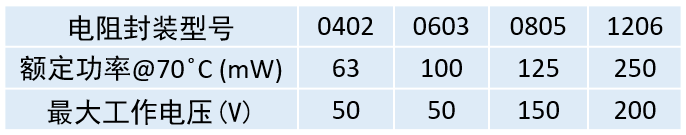

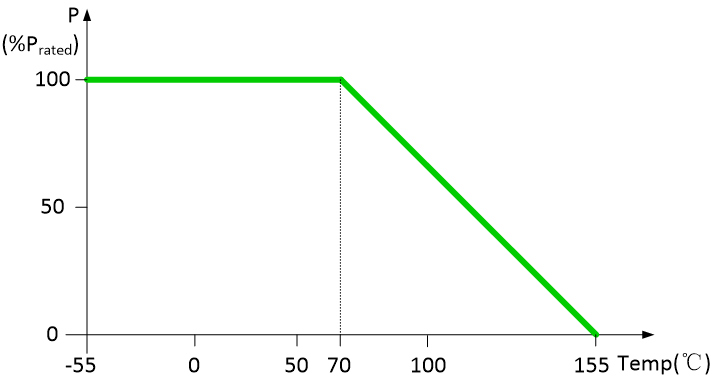

電阻選擇: 所選電阻耐壓��、最大功耗及溫度不能超出使用范圍。

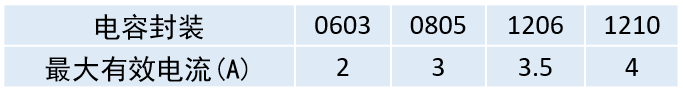

電容選擇: 選擇時也需要考慮所選電容的耐壓與最大有效電流���。

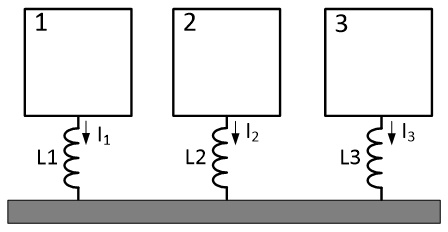

電感選擇: 所選電感有效值電流����、峰值電流必須大于實際電路中流過的電流�����。

電路設(shè)計常見干擾

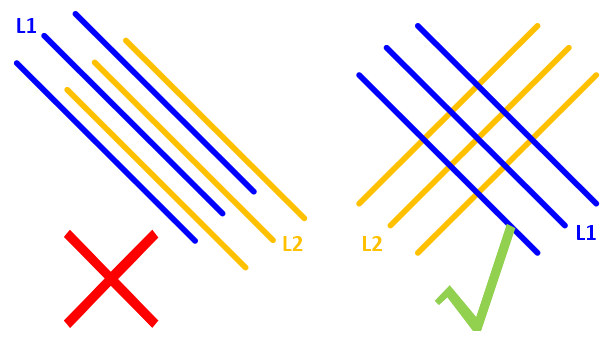

串?dāng)_: 設(shè)計線路平行走線距離過長時, 導(dǎo)線間的互容�����、互感將能量耦合至相鄰的傳輸線�?��?梢酝ㄟ^以下方法減少串?dāng)_影響:

1���、加入安全走線

2、實際時盡量讓相鄰走線互相垂直

3�、每走一段距離的平行線,增大兩者間的間距

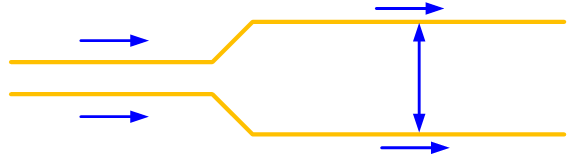

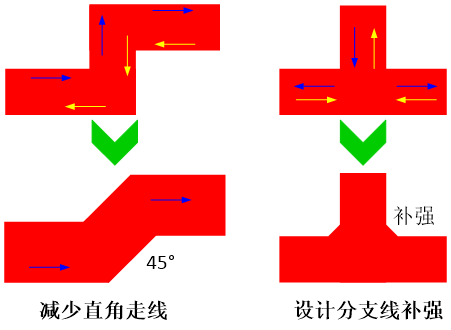

反射:由于布線的彎角��、分支太多造成傳輸線上阻抗不匹配,可以通過減少線路上的彎角及分支線或者避免直角走線及分支線補(bǔ)強(qiáng)來進(jìn)行改善���。

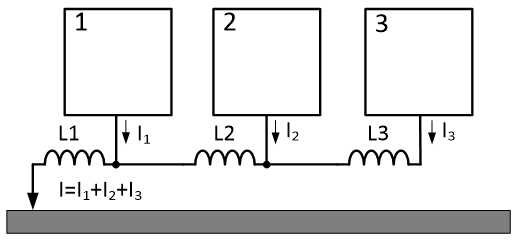

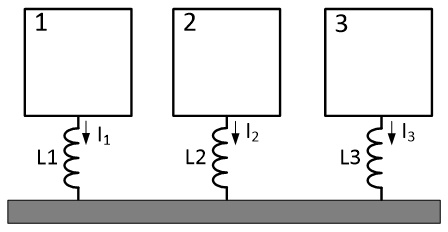

確定接地方式

單點(diǎn)接地(適用于低頻電路):所有的電路接地線接到公共地線同一點(diǎn)�, 接線簡單且減少地線回路相互干擾���。

,

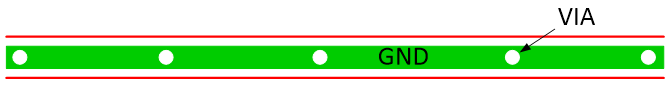

多點(diǎn)接地(適用于多層板電路/高頻電路):系統(tǒng)內(nèi)部各部分就近接地��,提供較低的接地阻抗����。

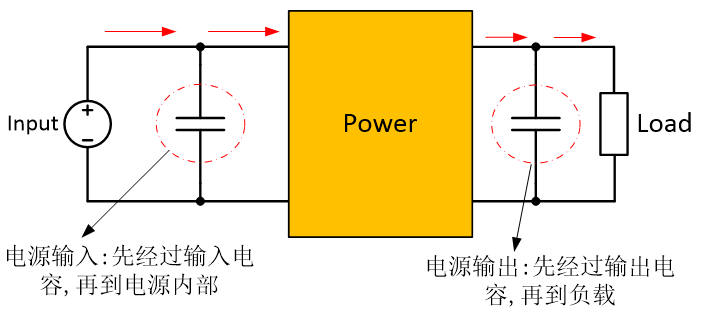

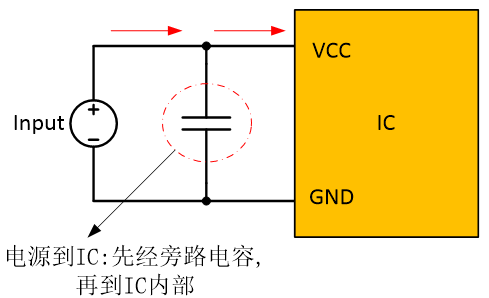

增加濾波�����、旁路電容

為保證輸入/輸出電壓穩(wěn)定�����,增加輸入/輸出電容�����。

在電源和IC間增加旁路電容�����,以保證輸入電壓穩(wěn)定并濾除高頻噪聲。

阻抗位置設(shè)計

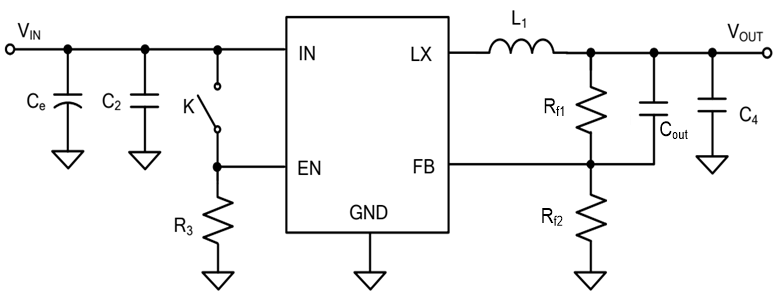

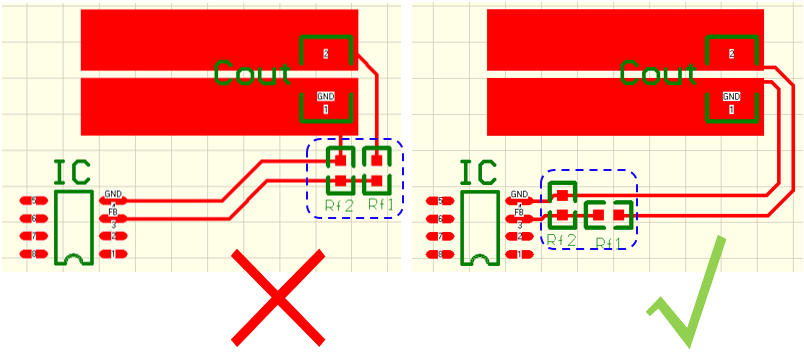

相對來說阻抗越高的位置, 越容易被干擾�。如下為一同步降壓芯片的PCB阻抗位置設(shè)計。

深圳宏力捷電子是一家專業(yè)從事電子產(chǎn)品電路板設(shè)計(layout布線設(shè)計)的PCB設(shè)計公司���,主要承接多層�、高密度的PCB設(shè)計畫板及電路板設(shè)計打樣業(yè)務(wù)�����。擁有平均超過10年工作經(jīng)驗的PCB設(shè)計團(tuán)隊����,能熟練運(yùn)用市場主流PCB設(shè)計軟件��,專業(yè)高效溝通保證PCB設(shè)計進(jìn)度�����,助您早一步搶占市場先機(jī)�����!

深圳宏力捷推薦服務(wù):PCB設(shè)計打樣 | PCB抄板打樣 | PCB打樣&批量生產(chǎn) | PCBA代工代料